▶ 배선 ( Wiring ) 이란 ?

배선 ( Wiring ) 이란 전자회로에서 정보등을 전송하기 위해 부품의

단자들을 상호 연결해 기판에 도전성을 형성한 것이다

▷ 배선 설계

드라이버(Driver) 에서 수신(Receiver) 측으로 신호라인(Signaling Line) 을 통해

정보가 전송될 때, 신호가 가지고 있는 성질을 유지하면서 내 외부적인 방해요소

없이 정확하게 정보를 전달할 수 있도록 단자를 결선 하는 것이다

▷ 신호 라인(Signaling Line) 간읙 간섭의 발생

▶ 배선 설계의 기본

레이아웃(Layout) 설계 혹은 패턴(Pattern)의 설계라고 보면 된다

라우팅(Routing) 이라고도 하고, 패턴의 폭(W) 은 일정하게 그리지만 정해진 규격은 없다

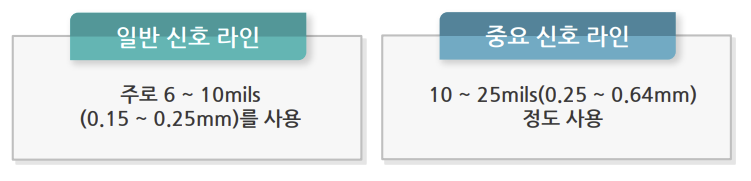

일반 신호 라인은 6~10 [mils] 를 사용하고

중요 신호 라인은 10~25 [mils] 를 사용한다

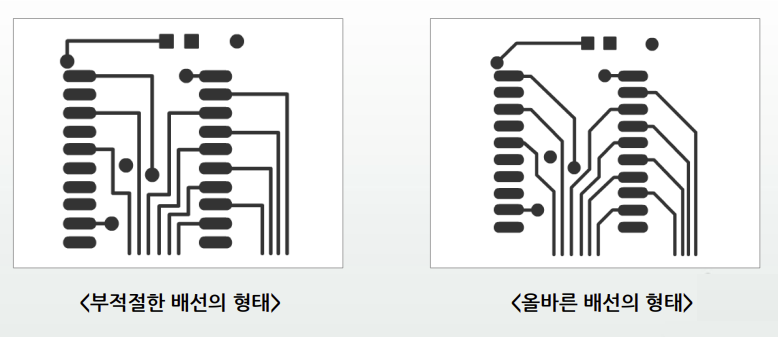

▷ 배선의 형태

배선의 형태는 90' 보다는 45' 로 인출 될 수 있도록 설계해야 한다

90' 배선 형태는 방사 현상이 발생할 가능성이 높기 때문이다

▷ 배선의 분기

배선의 분기(Branch) 는 가능한 부품의 패드(Pad) 나 비아(Via) 가 있는 곳에서 실행한다

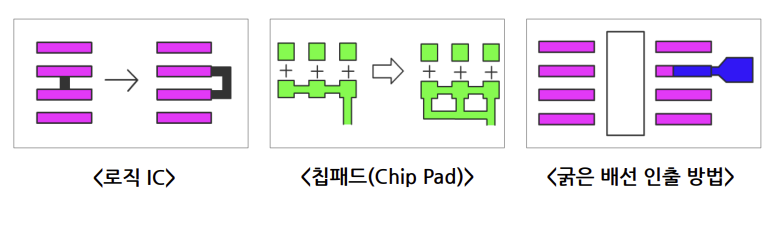

▷ SMD(Surface Mounting Device) 배선의 인출 방법

패드(Pad) 의 굵기 보다 크게 인출하면 안 되며, 패드의 굵기와 같거나 작게 끔 인출해야 한다

패드(Pad) 간의 연결 방법은 패드의 바깥쪽에서 배선 한다

패드의 굵기보다 큰 배선의 경우에는, 패드의 굵기와 같게 하여 최대한 짧게 인출한다

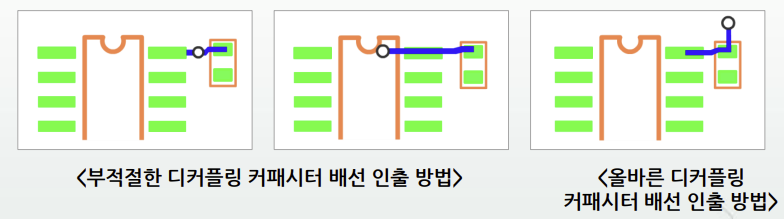

▷ 디커플링 커패시터 (Decoupling Capacitor) 배선의 인출 방법

Logic IC 의 전원 단자는 반드시 디커플링 커패시터를 거친 후 들어갈 수 있도록

해야한다. 디커플링 커패시터는 Logic IC 전원 단자에 가깝게 배치해야 한다

▶ 중요신호라인

▷ 클럭 라인( Clock Line ), 설계시

디지털회로에서 일정한 파형을 생성해, 순차논리회로 등에서

시스템이 하는 모든 일의 순서와 타이밍을 정해주는 신호 이다

종류는 오실레이터(Oscilator), 크리스탈(Crystal) 등이 있고

배선 설계는 짧고 굵게 하며, 형태는 직선이 되도록 해야한다

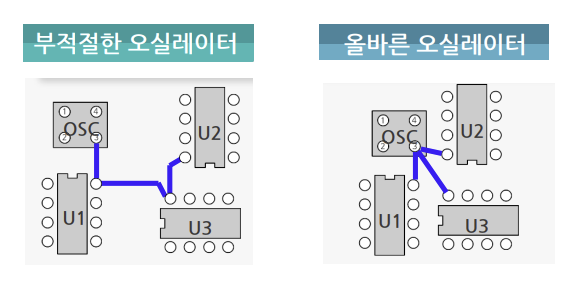

-오실레이터(Oscilator), 설계 시

부적절한 오실레이터에서 클럭라인(Clock Line, 파란선) 의 길이가 다소 길다. 이렇게되면

클럭 라인이 U1, U3 에서는 정상작동 하더라도 U2 라인에서는 문제가 발생할 수 있다

그래서, 오른쪽 설계처럼 클럭 라인이 잘 분배되도록 설계 해야 한다. 클럭 라인의 길이가

대체로 짧아져 문제가 발생될 가능성이 매우 낮아진다

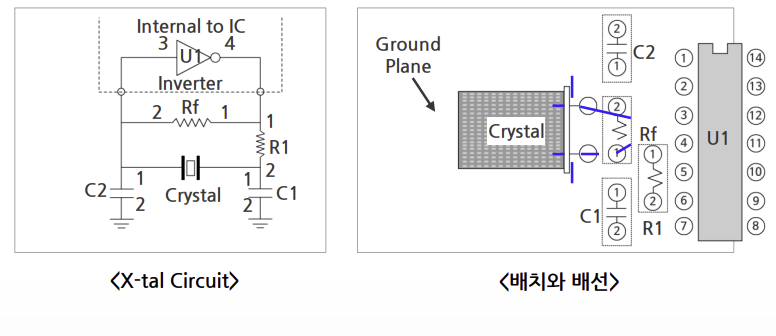

-크리스탈(X-tal), 설계 시

U1, Crystal, Rf, R1 이 20 [mm] 이내에 배선되도록 해야한다

배선 폭은 12~20 [mils] 정도가 적당하다

▷ 고속 신호 라인( High Speed Line ), 설계시

고속 신호 라인은 저항성분보다 인덕턴스가 높다

→ 도체가 굵고 짧을수록 저항, 인덕턴스가 작아진다

고속 신호 라인이 길어지는 경우는 인덕턴스가 증가해, 임피던스가 높아진다

→ 높은 임피던스는 전압강하로 이어져 고속 신호 라인이 길지 않도록 제한해야 한다

고속 신호 라인 간에 간에 간섭이 우려될 경우 Ground 를 사용해 고속 신호 라인 사이에

삽입하고, 고속 신호 라인의 클럭 라인은 Ground 가 인접되도록 하여 노이즈를 제거해야한다

신호 라인의 각도는 임피던스의 연속성을 위하여 가능한 예각 으로 설게한다

▶ 배선 설계의 주의 사항

주파수가 높은 클럭 라인(Clock Line) 은 인접한 신호 라인과 충분한 이격거리 확보

→ 양산 제품의 클럭 라인은 가드 트레이스 형태로 해 감싼다

클럭 부품(OSC, X-tal) 은 아래에 그라운드를 형성하여 노이즈에 적극적으로 대처 한다

주파수가 높은 클럭 라인(Clock Line) 이 아날로그 입력부를 지나갈 때에는

충분한 간격을 두고 유지해야 한다

신호 라인에 대해 비아 홀의 수를 줄여야 하고, 성지링 서로 다른 신호 라인 간에

길이를 제한해야 한다. 패턴의 형태는 45' 를 유지 한다

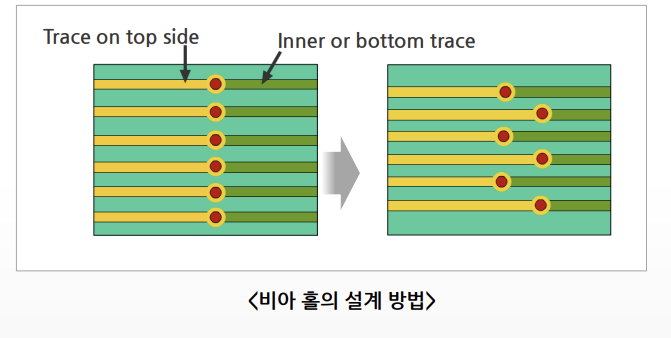

▷ 비아 홀( Via Hole ), 설계 시

비아 홀(Via Hole) 을 나란히 배치하는 경우에는 비아 홀 간의 간섭이 발생할 경우가

높으므로, 교차 방법으로 비아 홀 간의 간섭을 줄여야 한다

'회로 설계(Circuit Design) > PCB설계' 카테고리의 다른 글

| PCB, 층 배열(Layer Stack up), 층 배열 구조 (1) | 2023.01.30 |

|---|---|

| PCB, 노이즈(Noisy) 경로, 침입 경로 파악 (0) | 2023.01.27 |

| PCB설계, 부품 배치시 설계기준, 부품 특성별 위치 결정 (0) | 2022.12.14 |

| PCB설계, 수동소자(Passive element)의 이해 (0) | 2022.12.07 |

| PCB 설계의 기본 규칙, PCB 라우팅(Routing) (0) | 2022.11.17 |